Эльбрус/архитектура: различия между версиями

м (→Ссылки: +1 через EntityFX: http://habr.com/ru/post/534296/) |

м (→Версии: 2021: приближаются поставки 8СВ) |

||

| Строка 12: | Строка 12: | ||

* '''v3: "[[Эльбрус-4С]]" (предыдущая)''' ''<small>e4c, он же e2s</small>'' | * '''v3: "[[Эльбрус-4С]]" (предыдущая)''' ''<small>e4c, он же e2s</small>'' | ||

* '''v4: "[[Эльбрус-8С]]", "[[Эльбрус-1С+]]" (актуальная)''' ''<small>e8c, он же p1; и e1cp, он же e1c+ или p2</small>'' | * '''v4: "[[Эльбрус-8С]]", "[[Эльбрус-1С+]]" (актуальная)''' ''<small>e8c, он же p1; и e1cp, он же e1c+ или p2</small>'' | ||

* v5: "[[Эльбрус-8СВ]]" ( | * v5: "[[Эльбрус-8СВ]]" (опытная серия, расширенные векторные вычисления) ''<small>e8c2, он же p9</small>'' | ||

* v6: "[[Эльбрус-16С]]", "[[Эльбрус-12С]]", "[[Эльбрус-2С3]]" ([https://www.youtube.com/watch?v=f_hwK0zM9y8&t=24m25s | * v6: "[[Эльбрус-16С]]", "[[Эльбрус-12С]]", "[[Эльбрус-2С3]]" (инженерные образцы, [https://www.youtube.com/watch?v=f_hwK0zM9y8&t=24m25s аппаратная виртуализация]) ''<small>e16c, e12c, e2c3</small>'' | ||

== Совместимость == | == Совместимость == | ||

Версия от 11:20, 15 января 2021

Архитектура "Эльбрус"

Оригинальная 64-битная Little Endian VLIW; также известна как "Эльбрус-2000" (сокращённо e2k).

Не путать со SPARC и иными RISC, а также x86 (CISC).

Версии

Микропроцессоры "Эльбрус" различаются версиями микроархитектуры и системы команд; на июль 2019 года известны следующие:

- v2: "Эльбрус-2С+", "Эльбрус-2СМ" (устарела с лета 2018, нет поддержки в OSL после 3.0-rc35, где ядро 3.14.79 и компилятор 1.21.25)

- v3: "Эльбрус-4С" (предыдущая) e4c, он же e2s

- v4: "Эльбрус-8С", "Эльбрус-1С+" (актуальная) e8c, он же p1; и e1cp, он же e1c+ или p2

- v5: "Эльбрус-8СВ" (опытная серия, расширенные векторные вычисления) e8c2, он же p9

- v6: "Эльбрус-16С", "Эльбрус-12С", "Эльбрус-2С3" (инженерные образцы, аппаратная виртуализация) e16c, e12c, e2c3

Совместимость

В процессе портирования Альта была отмечена отличная практическая совместимость процессоров четвёртого поколения с бинарным кодом e2kv3, включая ядро, видеоподсистему и даже бинарный транслятор; официально она не гарантируется, хотя неофициально и подтверждается.

Производительность

При сборке под e2k для производительности и совместимости следует применять компилятор, настроенный под конкретную версию архитектуры (начиная с lcc 1.23 -- возможна настройка и под конкретный процессор).

При этом разница по 7za b, собранным под v3 и v4, на v4 составила у нас порядка процента.

Известно, что при переходе на e2kv6 "штраф" бинарникам, оптимизированным под предыдущие версии архитектуры, в ряде случаев вырастет, т.к. вследствие значительного роста тактовой частоты сильно изменятся планируемые задержки при работе с памятью и не ожидающий этого код будет чаще попадать на останов конвейера.

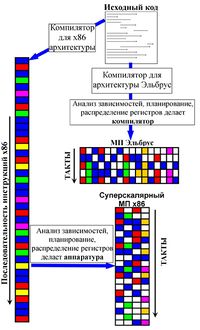

В то время как компилируемый код благодаря большим возможностям оптимизации (в т.ч. выявления и задействования скрытого параллелизма) во время компиляции находится в потенциально выигрышном положении по сравнению с суперскалярными архитектурами, виртуальные машины для байткода и интерпретаторы симметрично находятся в положении проигрышном (для их работы характерна высокая степень зависимости по данным в циклах). Это стоит учитывать при планировании разработки.

Ссылки

- Руководство по эффективному программированию на платформе «Эльбрус»

- Краткое описание архитектуры Эльбрус

- Микропроцессоры и вычислительные комплексы семейства «Эльбрус» (книга, PDF)

- Безопасная среда исполнения критических приложений во встраиваемых системах на базе вычислительных средств семейства «Эльбрус» (PDF)

- МЦСТ > Тэги > Архитектура микропроцессоров

- Вычислительная платформа «Эльбрус» и её практическое применение (SECR-2018)

- Оптимизация кода для платформы Эльбрус на простых примерах

- Портирование JS на Эльбрус

- inxi: Elbrus CPU support data and implementation

- Что такое процессор "Эльбрус"? История создания. Где применяется?

- Микроархитектура восьмиядерного универсального микропроцессора «Эльбрус-8C»