Эльбрус/архитектура: различия между версиями

м (→Ссылки: +1) |

м (→Версии: s/e32c/e48c/) |

||

| (не показано 37 промежуточных версий 3 участников) | |||

| Строка 1: | Строка 1: | ||

[[Файл:Elbrus arch.jpg|right|200px]] | |||

= Архитектура "Эльбрус" = | = Архитектура "Эльбрус" = | ||

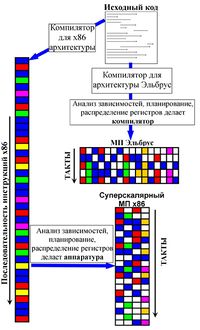

Оригинальная 64-битная Little Endian VLIW; также известна как "Эльбрус-2000" (сокращённо e2k). | Оригинальная 64-битная Little Endian VLIW; также известна как "Эльбрус-2000" (сокращённо e2k). | ||

Не путать со SPARC и иными RISC, а также x86 (CISC). | [[эльбрус/faq|Не путать]] со SPARC и иными RISC, а также x86 (CISC). | ||

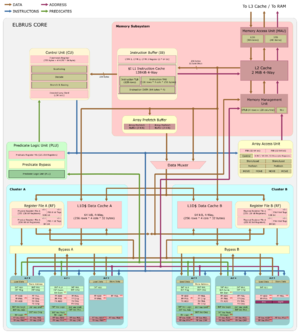

[[Файл:E2k arch m.png|мини|right|Архитектура ядра Эльбрус]] | |||

== Версии == | == Версии == | ||

[[Модели процессоров Эльбрус|Микропроцессоры "Эльбрус"]] различаются версиями микроархитектуры и системы команд; на | [[Модели процессоров Эльбрус|Микропроцессоры "Эльбрус"]] различаются версиями микроархитектуры и системы команд; на март 2022 года известны следующие: | ||

* v2: "Эльбрус-2С+", "Эльбрус-2СМ" <small>(устарела с лета 2018 | * v2: "[[Эльбрус-2С+]]", "Эльбрус-2СМ" <small>(устарела с лета 2018<ref>нет поддержки в OSL после 3.0-rc35, где ядро 3.14.79 и компилятор 1.21.25</ref>)</small> | ||

* | * v3: "[[Эльбрус-4С]]" (уходящая) ''<small>e4c, он же e2s</small>'' | ||

* '''v4: "Эльбрус-8С", "Эльбрус-1С+" | * '''v4: "[[Эльбрус-8С]]", "[[Эльбрус-1С+]]"''' (предыдущая серийная) ''<small>e8c, он же p1; и e1cp, он же e1c+ или p2</small>'' | ||

* v5: "Эльбрус-8СВ" ( | * '''v5: "[[Эльбрус-8СВ]]"''' (серийная, расширенные векторные вычисления) ''<small>e8c2, он же p9</small>'' | ||

* v6: "Эльбрус-16С", "Эльбрус-12С", "Эльбрус-2С3" ([https://www.youtube.com/watch?v=f_hwK0zM9y8&t=24m25s | * '''v6: "[[Эльбрус-16С]]", "[[Эльбрус-12С]]", "[[Эльбрус-2С3]]"''' (серийный 2С3, инженерные образцы 16С, [https://www.youtube.com/watch?v=f_hwK0zM9y8&t=24m25s аппаратная] [http://wiki.elbrus.ru/virt виртуализация]) ''<small>e16c, e12c, e2c3</small>'' | ||

* v7: "Эльбрус-48C", "Эльбрус-4C3" (перспективная) ''<small>e48c, e4c3</small>'' | |||

== Безопасность == | |||

Одной из ключевых особенностей e2k в любом режиме является наличие [http://habr.com/ru/company/embox/blog/447704/ трёх аппаратных стеков] -- с одной стороны это исключает срыв стека, с другой -- добавляет проблем при переносе ПО, которое пытается с предположительно единственным стеком крутить свои "штучки" (начиная с JIT). | |||

В [[эльбрус/ptr128|защищённом режиме]] добавляется тегирование памяти, исключая ещё и переполнение массива. | |||

== Совместимость == | == Совместимость == | ||

В процессе [[эльбрус/портирование|портирования]] Альта была отмечена отличная практическая [[эльбрус/совместимость|совместимость]] процессоров четвёртого поколения с бинарным кодом e2kv3, включая ядро, видеоподсистему и даже бинарный транслятор; официально она не гарантируется, хотя неофициально и [http://www.youtube.com/watch?v=Yy8RXtvcPJw&t=11m1s подтверждается]. | В процессе [[эльбрус/портирование|портирования]] Альта была отмечена отличная практическая [[эльбрус/совместимость|совместимость]] процессоров четвёртого поколения с бинарным кодом e2kv3, включая ядро, видеоподсистему и даже бинарный транслятор; официально она не гарантируется, хотя неофициально и [http://www.youtube.com/watch?v=Yy8RXtvcPJw&t=11m1s подтверждается]. | ||

Также наблюдается хорошая совместимость v5-машин с кодом v4+ и достаточная как минимум для [[rescue]]-образа работоспособность кода v3+ на v6. | |||

Это действительно для сборки с [[Эльбрус/оптимизация#-march/-mtune|<tt>-march</tt>, не <tt>-mtune</tt>]]. | |||

== Производительность == | == Производительность == | ||

| Строка 26: | Строка 40: | ||

Известно, что при переходе на e2kv6 "штраф" бинарникам, оптимизированным под предыдущие версии архитектуры, в ряде случаев вырастет, т.к. вследствие значительного роста тактовой частоты сильно изменятся планируемые задержки при работе с памятью и не ожидающий этого код будет чаще попадать на останов конвейера. | Известно, что при переходе на e2kv6 "штраф" бинарникам, оптимизированным под предыдущие версии архитектуры, в ряде случаев вырастет, т.к. вследствие значительного роста тактовой частоты сильно изменятся планируемые задержки при работе с памятью и не ожидающий этого код будет чаще попадать на останов конвейера. | ||

В то время как компилируемый код благодаря большим возможностям оптимизации (в т.ч. выявления и задействования скрытого параллелизма) во время компиляции находится в потенциально выигрышном положении по сравнению с суперскалярными архитектурами, виртуальные машины для байткода и интерпретаторы симметрично находятся в положении проигрышном (для их работы характерна высокая степень зависимости по данным в циклах). Это стоит учитывать при планировании разработки. | В то время как компилируемый код благодаря большим возможностям [[эльбрус/оптимизация|оптимизации]] (в т.ч. выявления и задействования скрытого параллелизма) во время компиляции находится в потенциально выигрышном положении по сравнению с суперскалярными архитектурами, виртуальные машины для байткода и интерпретаторы симметрично находятся в положении проигрышном (для их работы характерна высокая степень зависимости по данным в циклах). Это стоит учитывать при планировании разработки. | ||

= Ссылки = | = Ссылки = | ||

* [http:// | * [http://mcst.ru/elbrus_prog Руководство по эффективному программированию на платформе «Эльбрус»] | ||

** [http://ftp.altlinux.org/pub/people/mike/elbrus/docs/elbrus_prog/html/chapter10.html Система команд микропроцессора «Эльбрус»] | ** [http://ftp.altlinux.org/pub/people/mike/elbrus/docs/elbrus_prog/html/chapter10.html Система команд микропроцессора «Эльбрус»] | ||

* [http://www.elbrus.ru/elbrus_arch Краткое описание архитектуры Эльбрус] | * [http://www.elbrus.ru/elbrus_arch Краткое описание архитектуры Эльбрус] | ||

* [http:// | * [http://old.mcst.ru/doc/book_121130.pdf Микропроцессоры и вычислительные комплексы семейства «Эльбрус»] (книга, [http://mcst.ru/files/511cea/886487/1a8f40/000000/book_elbrus.pdf PDF]) | ||

* [http:// | * [http://mcst.ru/files/5c9c8f/e30cd8/509328/000000/t.r._mustafin_a._i._alyohin_e.m._kravtsunov_b.o._makaev_bezopasnaya_sreda_ispolneniya_kriticheskih_prilozheniy_vo_vstraivaemyh_sistemah_na_baze_vychislitelnyh_sredstv_semeystva_elbrus.pdf Безопасная среда исполнения критических приложений во встраиваемых системах на базе вычислительных средств семейства «Эльбрус»] (PDF) | ||

* [http:// | * [http://mcst.ru/files/57571b/cf0cd8/50722d/000000/alfonsodemenkokozhin_i_dr-mikroarhitektura_vosmiyadernogo_mikroprotsessora.pdf Микроархитектура восьмиядерного универсального микропроцессора «Эльбрус-8C»] | ||

** [http:// | * [http://mcst.ru/files/5ef0c2/db0cd8/50c164/000001/d._znamenskiy_a._blinnikov_apparatnaya_podderzhka_virtualizatsii_arhitektury_elbrus.pdf Аппаратная поддержка виртуализации архитектуры «Эльбрус»] | ||

* [http://mcst.ru/tag/51a87e3564871aef1a000000 МЦСТ > Тэги > Архитектура микропроцессоров] | |||

** [http://mcst.ru/e2k_arch.shtml Основные принципы архитектуры Е2К] (2001) | |||

* [http://0x1.tv/20181012BB Вычислительная платформа «Эльбрус» и её практическое применение] (SECR-2018) | * [http://0x1.tv/20181012BB Вычислительная платформа «Эльбрус» и её практическое применение] (SECR-2018) | ||

* [http://telegra.ph/O-sovetskom-proishozhdenii-VLIW-08-16 О советском происхождении VLIW] (тж. [http://habr.com/ru/post/573306/ Вектор-инструкция: о советском происхождении VLIW]; Пётр Советов) | |||

* [https://habr.com/ru/company/smartengines/blog/317672/ Оптимизация кода для платформы Эльбрус на простых примерах] | * [https://habr.com/ru/company/smartengines/blog/317672/ Оптимизация кода для платформы Эльбрус на простых примерах] | ||

* [https://habr.com/ru/company/jugru/blog/419155/ Портирование JS на Эльбрус] | * [https://habr.com/ru/company/jugru/blog/419155/ Портирование JS на Эльбрус] | ||

* [https://habr.com/ru/company/oleg-bunin/blog/584628/ Архитектура и особенности процессора Эльбрус 2000] | |||

* [https://github.com/smxi/inxi/issues/197 inxi: Elbrus CPU support data and implementation] | * [https://github.com/smxi/inxi/issues/197 inxi: Elbrus CPU support data and implementation] | ||

* [http://trueconf.ru/blog/wiki/chto-takoe-proczessor-elbrus Что такое процессор "Эльбрус"? История создания. Где применяется?] | * [http://trueconf.ru/blog/wiki/chto-takoe-proczessor-elbrus Что такое процессор "Эльбрус"? История создания. Где применяется?] | ||

* [http://zen.yandex.ru/media/electromozg/filosofiia-arhitektury-rossiiskogo-processora-elbrus-v-chem-ego-fishka-60351f8e2dc57956366c8bb1 Философия архитектуры российского процессора Эльбрус. В чём его фишка?] | |||

* [http://www.ixbt.com/cpu/e2k-spec.html Эльбрус Бабаяна и Pentium Пентковского] <!-- http://web.archive.org/web/19991115185234/http://developer.intel.com/technology/itj/q21999/articles/art_2who.htm: Vladimir Pentkovski is a Principal Engineer in the Microprocessor Product Group in Folsom. He was one of the architects in the core team, which defined the Internet Streaming SIMD Extensions of IA-32 architecture. Vladimir led the development of Pentium III processor architecture and performance analysis. Previously he led the development of compilers and software and hardware support for programming languages for Elbrus multi-processor computers in Russia. Vladimir holds a Doctor of Science degree and Ph.D. degree in computer science and engineering from Russia. His e-mail is vladimir.m.pentkovski@intel.com. --> | |||

* [http://t.me/e2k_chat/89326 Так что у VLIW/EPIC ровно один наблюдаемый прогрессивной общественностью недостаток: это российская разработка. Повторюсь, никогда такого не было...] | |||

* [http://github.com/nrdmn/elbrus-docs elbrus-docs] ''попытка разобраться со стороны'' | |||

* [http://www.iakovlev.org/index.html?p=8912&m=1&l1=7 iakovlev.org] ''попытка обобщить одной страницей'' | |||

* [http://arrowd.name/posts/2022-09-05-elbrus-playground.html Setting up a FreeBSD playground for Elbrus2000 architecture] | |||

* [http://github.com/ilyakurdyukov/hello-asm hello-asm: примеры для Эльбруса на все режимы указателей (32, 64, 128)] | |||

* [http://руни.рф/index.php/Эльбрус_(процессорная_архитектура) Эльбрус (процессорная архитектура)] | |||

* [http://old.redstar.ru/2001/03/01_03/r_or21.html Покорение «Эльбруса»] | |||

{{Category navigation|title=Модели процессоров Эльбрус|category=Модели процессоров Эльбрус|sortkey=*}} | {{Category navigation|title=Модели процессоров Эльбрус|category=Модели процессоров Эльбрус|sortkey=*}} | ||

{{Category navigation|title=E2K|category=E2K|sortkey=*}} | {{Category navigation|title=E2K|category=E2K|sortkey=*}} | ||

Текущая версия от 18:24, 3 июля 2024

Архитектура "Эльбрус"

Оригинальная 64-битная Little Endian VLIW; также известна как "Эльбрус-2000" (сокращённо e2k).

Не путать со SPARC и иными RISC, а также x86 (CISC).

Версии

Микропроцессоры "Эльбрус" различаются версиями микроархитектуры и системы команд; на март 2022 года известны следующие:

- v2: "Эльбрус-2С+", "Эльбрус-2СМ" (устарела с лета 2018[1])

- v3: "Эльбрус-4С" (уходящая) e4c, он же e2s

- v4: "Эльбрус-8С", "Эльбрус-1С+" (предыдущая серийная) e8c, он же p1; и e1cp, он же e1c+ или p2

- v5: "Эльбрус-8СВ" (серийная, расширенные векторные вычисления) e8c2, он же p9

- v6: "Эльбрус-16С", "Эльбрус-12С", "Эльбрус-2С3" (серийный 2С3, инженерные образцы 16С, аппаратная виртуализация) e16c, e12c, e2c3

- v7: "Эльбрус-48C", "Эльбрус-4C3" (перспективная) e48c, e4c3

Безопасность

Одной из ключевых особенностей e2k в любом режиме является наличие трёх аппаратных стеков -- с одной стороны это исключает срыв стека, с другой -- добавляет проблем при переносе ПО, которое пытается с предположительно единственным стеком крутить свои "штучки" (начиная с JIT).

В защищённом режиме добавляется тегирование памяти, исключая ещё и переполнение массива.

Совместимость

В процессе портирования Альта была отмечена отличная практическая совместимость процессоров четвёртого поколения с бинарным кодом e2kv3, включая ядро, видеоподсистему и даже бинарный транслятор; официально она не гарантируется, хотя неофициально и подтверждается.

Также наблюдается хорошая совместимость v5-машин с кодом v4+ и достаточная как минимум для rescue-образа работоспособность кода v3+ на v6.

Это действительно для сборки с -march, не -mtune.

Производительность

При сборке под e2k для производительности и совместимости следует применять компилятор, настроенный под конкретную версию архитектуры (начиная с lcc 1.23 -- возможна настройка и под конкретный процессор).

При этом разница по 7za b, собранным под v3 и v4, на v4 составила у нас порядка процента.

Известно, что при переходе на e2kv6 "штраф" бинарникам, оптимизированным под предыдущие версии архитектуры, в ряде случаев вырастет, т.к. вследствие значительного роста тактовой частоты сильно изменятся планируемые задержки при работе с памятью и не ожидающий этого код будет чаще попадать на останов конвейера.

В то время как компилируемый код благодаря большим возможностям оптимизации (в т.ч. выявления и задействования скрытого параллелизма) во время компиляции находится в потенциально выигрышном положении по сравнению с суперскалярными архитектурами, виртуальные машины для байткода и интерпретаторы симметрично находятся в положении проигрышном (для их работы характерна высокая степень зависимости по данным в циклах). Это стоит учитывать при планировании разработки.

Ссылки

- Руководство по эффективному программированию на платформе «Эльбрус»

- Краткое описание архитектуры Эльбрус

- Микропроцессоры и вычислительные комплексы семейства «Эльбрус» (книга, PDF)

- Безопасная среда исполнения критических приложений во встраиваемых системах на базе вычислительных средств семейства «Эльбрус» (PDF)

- Микроархитектура восьмиядерного универсального микропроцессора «Эльбрус-8C»

- Аппаратная поддержка виртуализации архитектуры «Эльбрус»

- МЦСТ > Тэги > Архитектура микропроцессоров

- Вычислительная платформа «Эльбрус» и её практическое применение (SECR-2018)

- О советском происхождении VLIW (тж. Вектор-инструкция: о советском происхождении VLIW; Пётр Советов)

- Оптимизация кода для платформы Эльбрус на простых примерах

- Портирование JS на Эльбрус

- Архитектура и особенности процессора Эльбрус 2000

- inxi: Elbrus CPU support data and implementation

- Что такое процессор "Эльбрус"? История создания. Где применяется?

- Философия архитектуры российского процессора Эльбрус. В чём его фишка?

- Эльбрус Бабаяна и Pentium Пентковского

- Так что у VLIW/EPIC ровно один наблюдаемый прогрессивной общественностью недостаток: это российская разработка. Повторюсь, никогда такого не было...

- elbrus-docs попытка разобраться со стороны

- iakovlev.org попытка обобщить одной страницей

- Setting up a FreeBSD playground for Elbrus2000 architecture

- hello-asm: примеры для Эльбруса на все режимы указателей (32, 64, 128)

- Эльбрус (процессорная архитектура)

- Покорение «Эльбруса»

- ↑ нет поддержки в OSL после 3.0-rc35, где ядро 3.14.79 и компилятор 1.21.25